Tiny Tapeout > Tiny Tapeout Chips > Tiny Tapeout SKY 25b > 450 VGA Screensaver with embedded bitmap ROM

450 VGA Screensaver with embedded bitmap ROM

450 : VGA Screensaver with embedded bitmap ROM

- Author: Uri Shaked

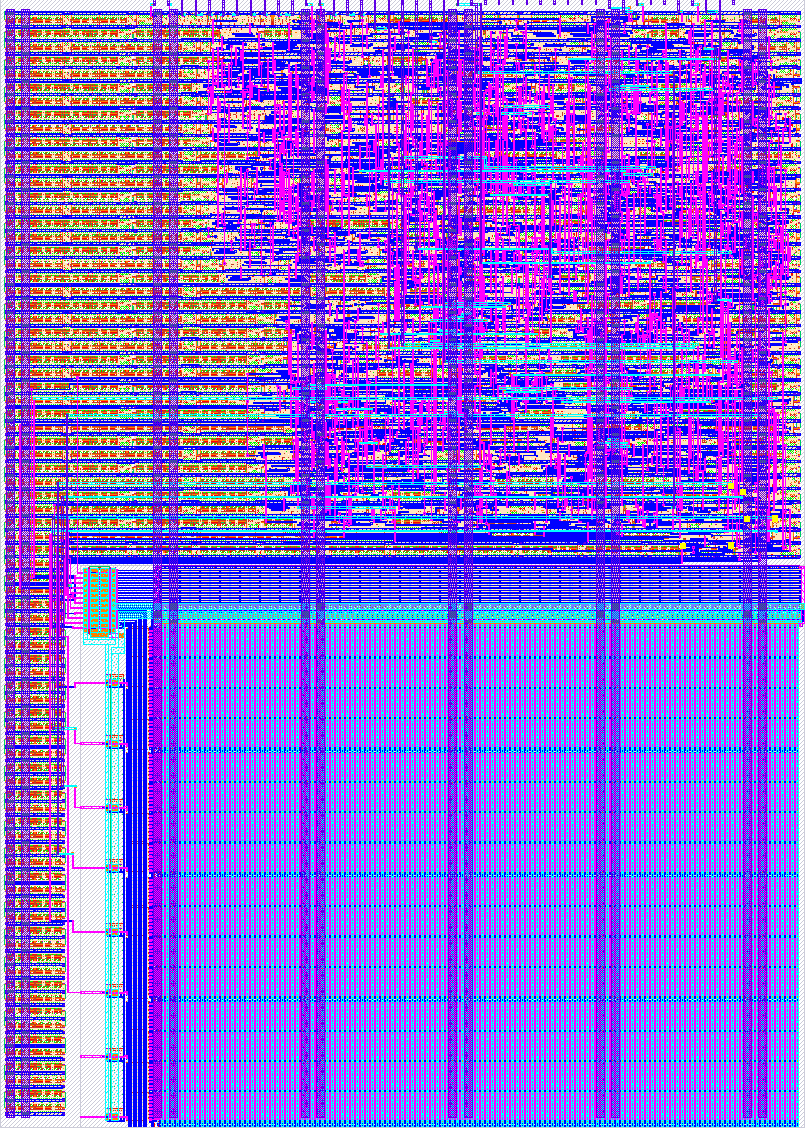

- Description: 64x64x6bpp Tiny Tapeout Logo bouncing around the screen (640x480, TinyVGA Pmod)

- GitHub repository

- Open in 3D viewer

- Open in VGA Playground

- Clock: 25175000 Hz

How it works

Displays a bouncing 64x64x6bpp Tiny Tapeout logo on the screen:

How to test

Connect to a VGA monitor. Set the following inputs to configure the design:

tile(ui_in[0]) to repeat the logo and tile it across the screendouble(ui_in[1]) to double the logo size to 128x128

If you have a Gamepad Pmod connected, you can also use the following controls:

- Start button: start/pause bouncing

- Left/right/up/down: change the bouncing direction (if bouncing) or move the logo around the screen (if paused)

External hardware

- Tiny VGA Pmod

- Optional: Gamepad Pmod

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | tile | R1 | |

| 1 | double | G1 | |

| 2 | B1 | ||

| 3 | VSync | ||

| 4 | gamepad_latch | R0 | |

| 5 | gamepad_clk | G0 | |

| 6 | gamepad_data | B0 | |

| 7 | HSync |