742 Wokwi Template

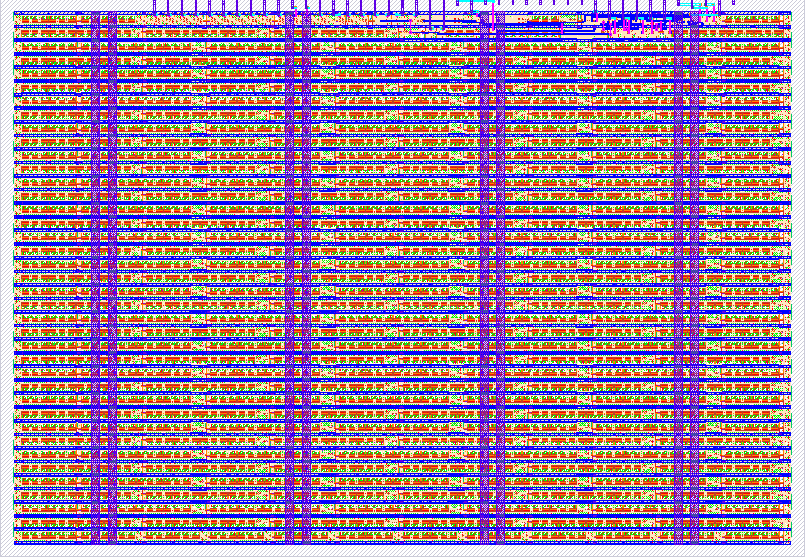

742 : Wokwi Template

- Author: Jonas Lehner

- Description: number output

- GitHub repository

- Open in 3D viewer

- View in Wokwi

- Clock: 0 Hz

How it works

Explain how your project works

If you switch the Lever 1 to 8 the 7-segment-LED will put out the number with the lever reset you will reset the led's. If you activate more than one lever there wont happen anything

How to test

Explain how to use your project If you switch the Lever 1 to 8 the 7-segment-LED will put out the number with the lever reset you will reset the led's. If you activate more than one lever there wont happen anything

External hardware

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | reset button | and inverter | |

| 1 | 1 lever | and and or | |

| 2 | 2 lever | and and or | |

| 3 | 3 lever | and and or | |

| 4 | 4 lever | and and or | |

| 5 | 5 lever | and and or | |

| 6 | 6 lever | and and or | |

| 7 | 7 lever | and and xor |