617 Gate-Level 8-bit MAC with Ripple-Carry Accumulator

617 : Gate-Level 8-bit MAC with Ripple-Carry Accumulator

- Author: Malik

- Description: Structurally-optimized unsigned 8-bit MAC unit from ML-guided design-space exploration, with 17-bit accumulator and serial command interface

- GitHub repository

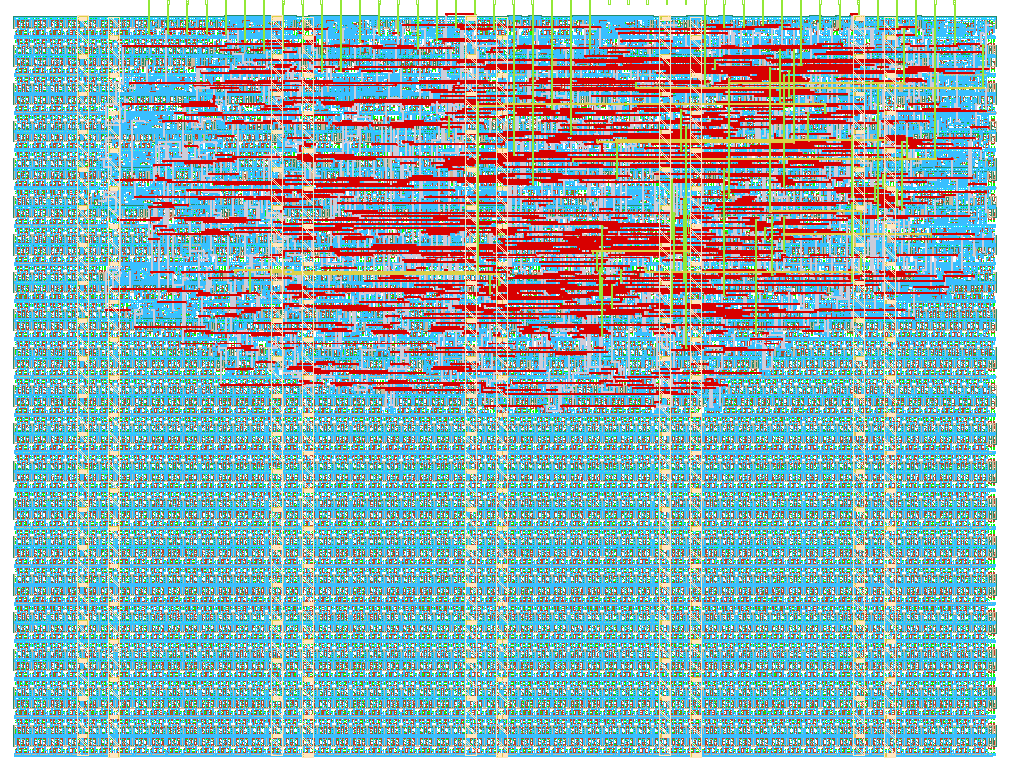

- Open in 3D viewer

- Clock: 50000000 Hz

Gate-Level 8-bit MAC with Ripple-Carry Accumulator

How it works

This design wraps a structurally-optimized gate-level multiply-accumulate (MAC) unit in a TinyTapeout-compatible clocked interface. The inner MAC core was produced through ML-guided design-space exploration of arithmetic architectures — it computes y[16:0] = a[7:0] * b[7:0] + c[15:0] as a purely combinational circuit using a ripple-carry accumulation structure.

The wrapper adds clocked operand registers, a 17-bit accumulator, and a serial command interface. On each MAC operation, the accumulator feeds back into the MAC's addend input, enabling running accumulation across multiple multiply-add cycles.

Specifications:

- Unsigned 8-bit × 8-bit multiply

- 17-bit accumulator (16-bit + carry/overflow)

- Single-cycle combinational MAC latency

- Gate-level optimized inner datapath

How to test

- Reset: Pull

rst_nlow then high. - Load A: Set

cmd=001, put value onui_in, clock once. - Load B + MAC: Set

cmd=010, put value onui_in, clock once. This triggersacc = a*b + acc. - Read result:

cmd=011for acc[7:0],cmd=100for acc[15:8],cmd=101for acc[16]. - Clear:

cmd=110zeros the accumulator. - Repeat steps 2-4 to accumulate more products.

Design context

The gate-level MAC netlist originates from a semester project on design-space exploration of AI hardware architectures, where ML-driven optimization was used to explore Pareto-optimal arithmetic unit implementations across power, performance, and area (PPA) tradeoffs.

External hardware

None required.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | data_in[0] | data_out[0] | cmd[0] |

| 1 | data_in[1] | data_out[1] | cmd[1] |

| 2 | data_in[2] | data_out[2] | cmd[2] |

| 3 | data_in[3] | data_out[3] | busy |

| 4 | data_in[4] | data_out[4] | overflow (acc[16]) |

| 5 | data_in[5] | data_out[5] | |

| 6 | data_in[6] | data_out[6] | |

| 7 | data_in[7] | data_out[7] |