234 One One

234 : One One

- Author: Gustav Kolind

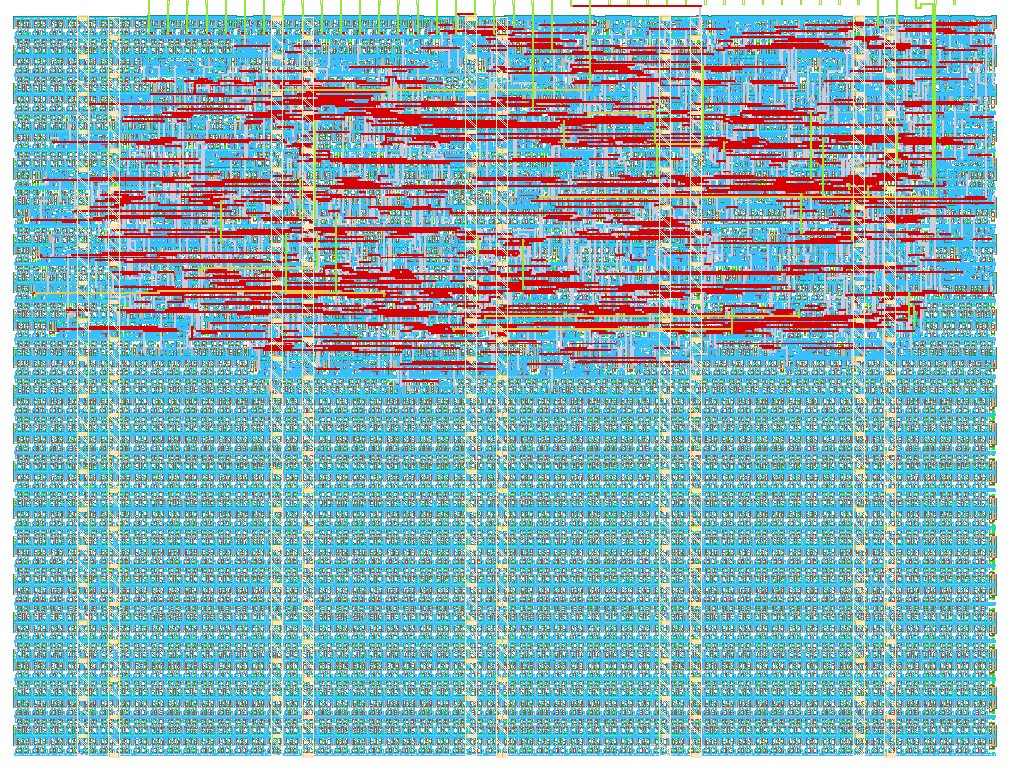

- Description: First Asic design, we will see where this goes

- GitHub repository

- Open in 3D viewer

- Clock: 0 Hz

How it works

The design receives a 1-bit serial input stream on ui[0], collects 16 bits into a sample, and applies either a low-pass or high-pass filter selected by ui[1]. The filtered sample is then shifted out serially on uo[0].

How to test

Apply reset, then drive input bits on ui[0] one bit per clock cycle. Set ui[1]=1 for low-pass or ui[1]=0 for high-pass before streaming starts. After the first 16-bit word is received, output bits begin appearing on uo[0] with pipeline delay.

External hardware

No external hardware is required.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | Waveform input | Filtered output | |

| 1 | Lowpass/Highpass select | ||

| 2 | |||

| 3 | |||

| 4 | |||

| 5 | |||

| 6 | |||

| 7 |