39 FPGA

39 : FPGA

- Author: Can Lehmann

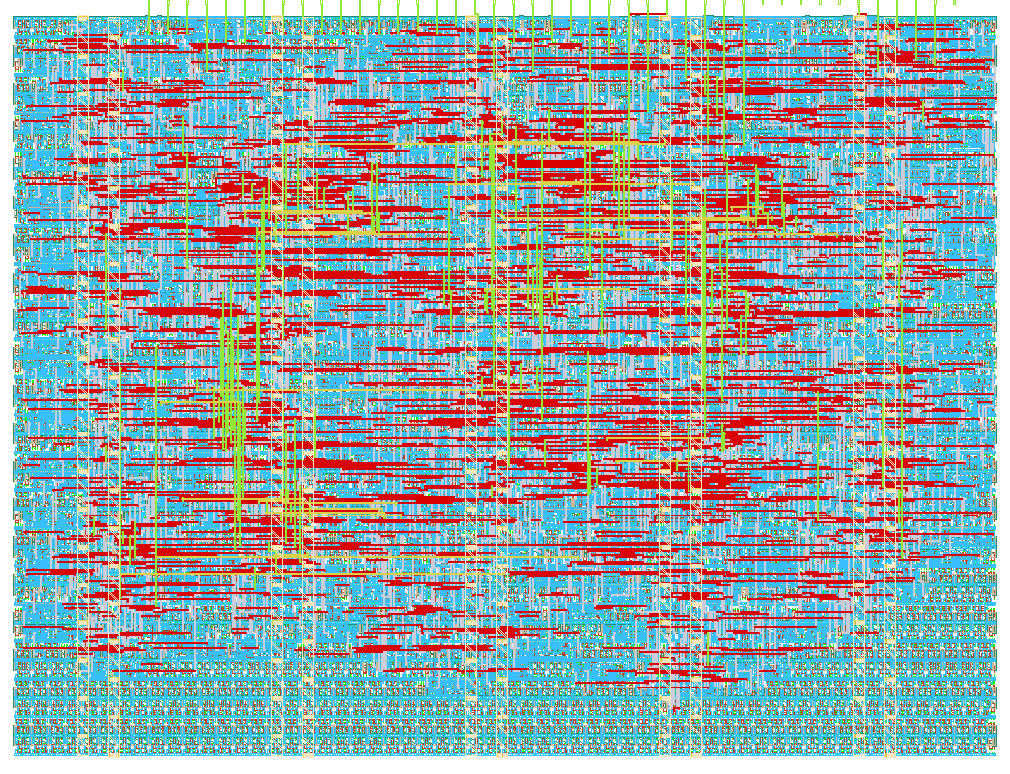

- Description: A tiny FPGA

- GitHub repository

- Open in 3D viewer

- Clock: 25000000 Hz

How it works

This project implements a tiny FPGA. The design is essentially a crossbar which connects 8 Inputs, 8 LUTs and 4 output ports. Because of the small size, I decided not to do any routing fabric besides the crossbar.

How to test

Important: Tie Virtual Reset high before powering on the chip.

- Tie the

Virtual Resetpin high to ensure that you don't accidentally get a combinatorial loop on startup. - Power on the chip.

- Load in a bitstream using the

Program DataandProgram Enablepins. The configuration is stored in a shift register, so you can load in the configuration one bit at a time. - Disable

Virtual Resetand observe your design in action!

Some of examples of what might be possible:

- Simple combinatorial logic.

- Toggling an output.

- A 4-bit counter that counts from 0 to 15 and then wraps around.

See the testbench for examples.

External hardware

No external hardware is required to run this project.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | Program Data | out[0] | in[0] |

| 1 | Program Enable | out[1] | in[1] |

| 2 | Virtual Reset | out[2] | in[2] |

| 3 | out[3] | in[3] | |

| 4 | in[4] | ||

| 5 | in[5] | ||

| 6 | in[6] | ||

| 7 | in[7] |