115 Silly demo

115 : Silly demo

- Author: James Buchanan

- Description: Zero to ASIC demo project

- GitHub repository

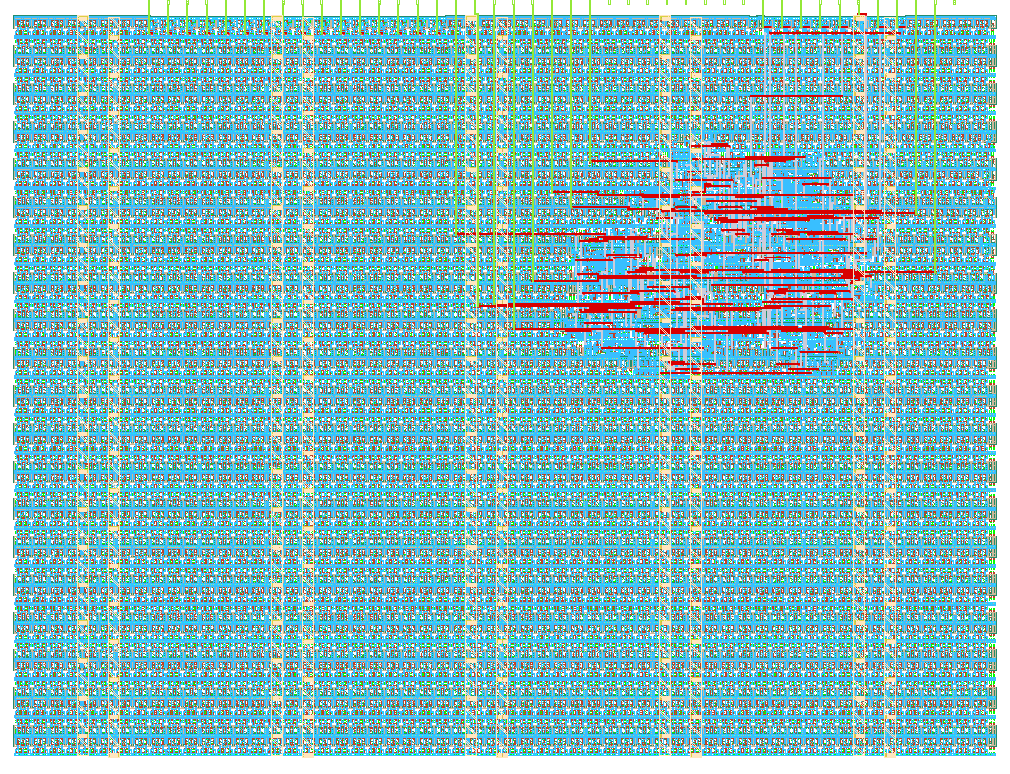

- Open in 3D viewer

- Clock: 10000000 Hz

How it works

silly2 creates divide by 2 clk signals, silly1 allows user to pick which signals get outputed.

How to test

Apply various signals onto the inputs and see what comes out the outputs. Outputs should be the appropriately divide by 2 clock.

External hardware

Use FPGA to drive and read signal outputs.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | ui_in[0] | uo_out[0] | |

| 1 | ui_in[1] | uo_out[1] | |

| 2 | ui_in[2] | uo_out[2] | |

| 3 | ui_in[3] | uo_out[3] | |

| 4 | ui_in[4] | uo_out[4] | |

| 5 | ui_in[5] | uo_out[5] | |

| 6 | ui_in[6] | uo_out[6] | |

| 7 | ui_in[7] | uo_out[7] |