874 Circulating register test

874 : Circulating register test

- Author: Mike Bell

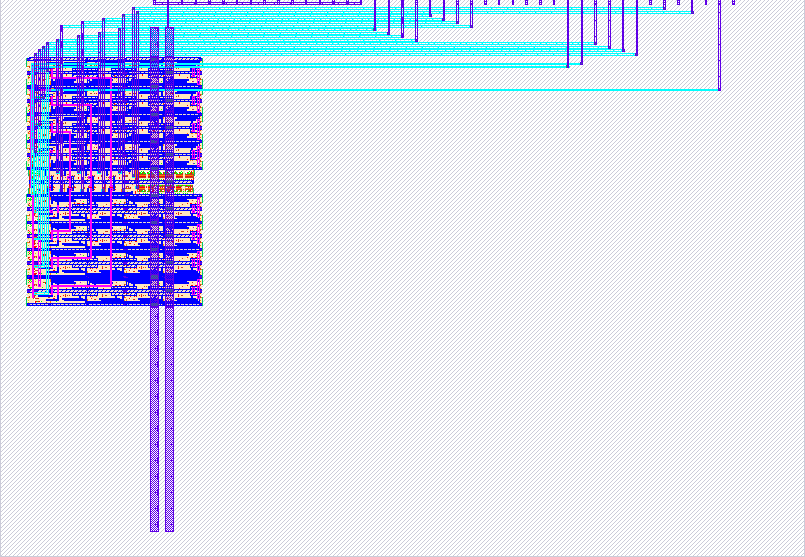

- Description: Test of a manually placed circulating register suitable for TinyQV's register file

- GitHub repository

- Open in 3D viewer

- Clock: 10 Hz

How it works

The project provides 2 32-bit registers that constantly cycle, in the same way as TinyQV's register file.

There's a 4-bit wide interface to the registers, a write enable for each register, and address selection for two read ports.

How to test

To write a register set its WEN high and clock data in over 8 cycles. To read a register select its address on one of the read ports and observe the data on the appropriate output over 4 cycles.

IO

| # | Input | Output | Bidirectional |

|---|---|---|---|

| 0 | Addr read port A | Data 0 port A | Write enable reg 0 |

| 1 | Data 1 port A | Write enable reg 1 | |

| 2 | Addr read port B | Data 2 port A | |

| 3 | Data 3 port A | ||

| 4 | Data 0 | Data 0 port B | |

| 5 | Data 1 | Data 1 port B | |

| 6 | Data 2 | Data 2 port B | |

| 7 | Data 3 | Data 3 port B |